# ULTRAFAST ANALOG-TO-DIGITAL CONVERTER USING RESONANT-TUNNELING TERNARY QUANTIZERS

T. Itoh, T. Waho, J. Osaka, H. Yokoyama and M. Yamamoto

NTT System Electronics Laboratories

3-1 Morinosato-Wakamiya, Atsugi-shi, Kanagawa, 243-01, Japan

## ABSTRACT

We study an analog-to-digital converter (ADC) that uses ternary quantizers consisting of resonant-tunneling diodes and HEMTs. This paper explains the ADC design and presents experimental results. A resonant-tunneling ternary quantizer operates at 10 GHz and a 2-bit ADC operates at 5 GHz.

## 1. INTRODUCTION

The application of resonant-tunneling diodes (RTD) to ultrafast circuits has been extensively investigated recently [1, 2, 3] because of the ultrafast switching speeds of RTDs [4] as well as their functionality, which leads to reduced circuit complexity. One possible application of these devices is an ultrafast analog-to-digital converter (ADC) [3, 5], which are attractive for wireless communications because they help realize the full potential of digital receivers. In addition, when resonant-tunneling diodes are connected in series, negative differential resistance results in multiple-peak I-V characteristics, which are well-suited for implementing multiple-valued logic (MVL) circuits [6]. MVL is expected to help make the circuit configuration simpler compared with conventional binary circuits. A compact ADC using quaternary quantizers has recently been presented with possible multi-GHz operation [7].

In this paper, we propose another approach to the

construction of ultrafast ADC, in which ternary quantizers are used instead of quaternary ones. By using ternary quantizers, we can enhance the operation margin and reduce the circuit voltage, while still maintaining the advantage of the MVL. This has led to the first experimental demonstration of an ultrafast operation of ADC with MVL circuits, which is described in this paper. We first explain the operation principle and then present experimental results for a 10-GHz HEMT-driven ternary quantizer and a 5-GHz 2-bit ADC.

## 2. PRINCIPLE OF ADC OPERATION WITH TERNARY QUANTIZERS

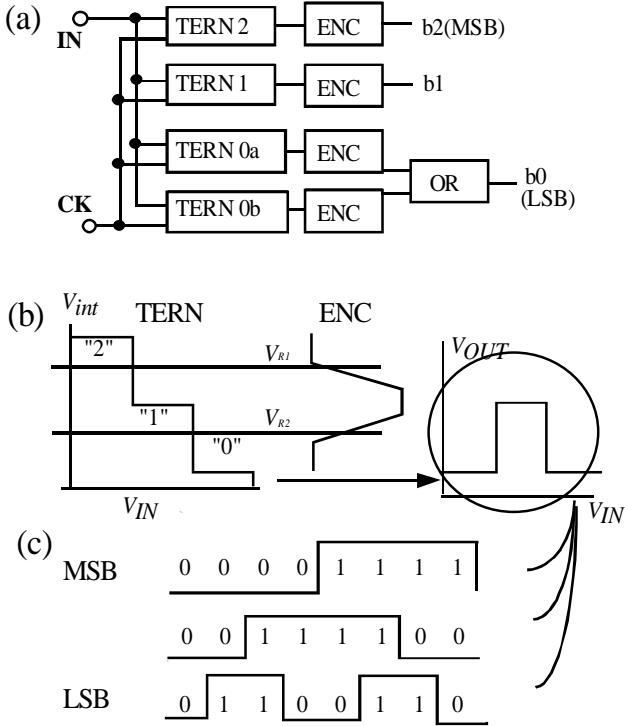

The ADC consists of ternary quantizers (TERNs), which quantize the input analog signal into three-level output. The TERNs are followed by encoding circuits (ENCs) that convert the ternary input to binary output. Figure 1(a) illustrates a block diagram of a 3-bit ADC, as an example. Figure 1(b) shows its operating principle and the functions of the TERNs and ENCs. TERN quantizes the input into three-level output, “0”, “1”, and “2”, with two threshold voltages. ENC then converts the three signals to “low”, “high”, and “low”, respectively. Using this low-high-low output as an element of the Gray code and suitably designing the threshold voltages, we can obtain a 3-bit Gray-code output, as depicted in Fig. 1(c). ADCs with 4-bit or

Fig. 1: (a) Block diagram, (b) schematic explanation, and (c) output binary code of a 3-bit ADC using ternary quantizers.

higher resolutions can be achieved in a similar manner.

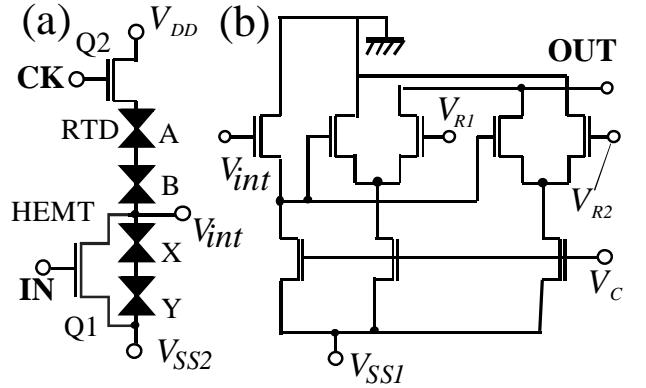

The ternary quantizer (TERN) is a monostable-to-multistable transition logic (MML) circuit [6] consisting of four RTDs (A, B, X, Y) and two HEMTs, Q1 and Q2 [Fig. 2 (a)]. Q1 is used to effectively modulate peak currents of RTDs X and Y while Q2 is used to supply a clock signal for the quantizer. An encoding circuit (ENC) contains eight HEMTs, and is comprised of a source-follower and a folding circuit based on differential amplifiers, as shown in Fig. 2(b). The output voltage of an ENC is “high” only for the input voltage between the two reference voltages  $V_{R1}$  and  $V_{R2}$  ( $V_{R1} < V_{R2}$ ), otherwise it is “low”.

Fig. 2: (a) Ternary quantizer TERN and (b) encoding circuit ENC.

### 3. EXPERIMENTS

#### 3.1 Fabrication

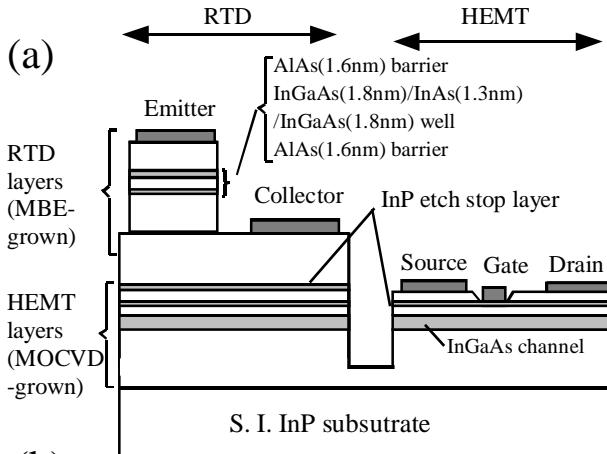

We integrated InGaAs/AlAs/InAs RTDs and InAlAs/InGaAs HEMTs on a semi-insulating InP substrate[8]. The cross-sectional view of a fabricated device is shown in Fig. 3 (a). The RTDs had a peak voltage of 0.3 V and a peak-to-valley current ratio of 10. Peak current density was  $9.5 \times 10^4$  A/cm<sup>2</sup> and the standard deviation of peak currents for a 4- $\mu$ m<sup>2</sup> RTD was as low as 3% over a 2-inch wafer. An InP recess etch-stop layer was inserted in a HEMT barrier layer. We used a MBE regrowth technique for RTD layers, which were grown on the MOCVD HEMT layers [9]. The gate length of the HEMT used was 0.7  $\mu$ m, the average threshold voltage was -0.50 V, and the standard deviation was 47 mV. The  $f_T$  of HEMT fabricated by a similar process was 40 GHz.

#### 3.2 2-bit ADC design

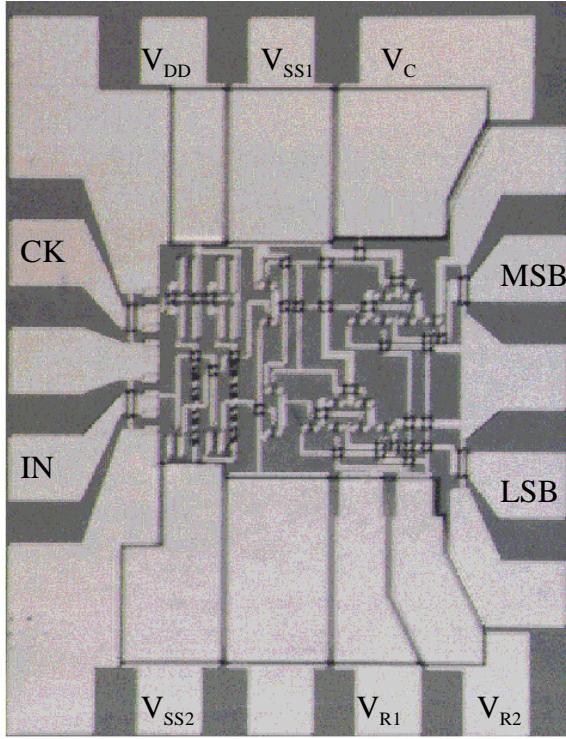

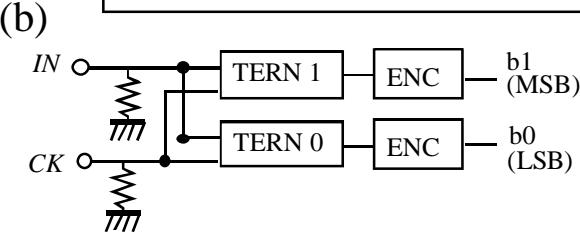

A block diagram and micrograph of the fabricated 2-bit ADC are shown in Figs. 3(b) and (c). In this ADC, we used RTD areas ranging from 4 to 9  $\mu$ m<sup>2</sup>

Fig. 3: (a) Cross-sectional view of fabricated devices, (b) block diagram of a 2-bit ADC, and (c) chip micrograph ( $1.0 \times 0.8 \text{ mm}^2$ ).

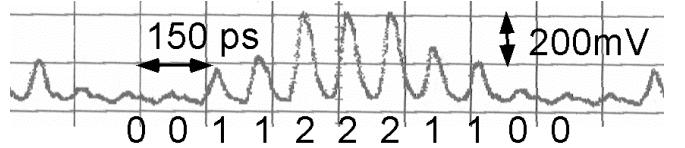

Fig. 4: Output waveform of a ternary quantizer.

(10 GHz)

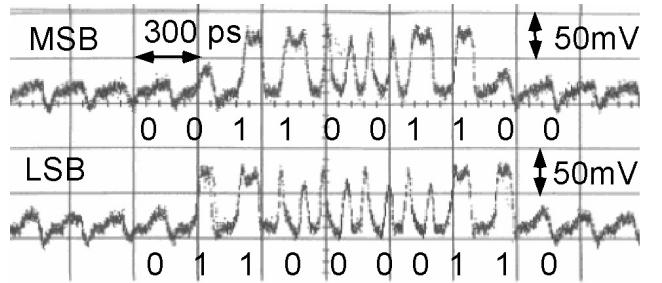

Fig. 5: Output waveforms of a 2-bit ADC (5 GHz).

to obtain the desired threshold voltages. The whole 2-bit ADC contained 8 RTDs and 20 HEMTs. The voltage sources were  $V_{DD} = 0 \text{ V}$ ,  $V_{SS1} = V_{SS2} = -3.2 \text{ V}$ ,  $V_C = -0.1 \text{ V}$ ,  $V_{R1} = -2.3 \text{ V}$ , and  $V_{R2} = -1.4 \text{ V}$ .

### 3.3 Measurement results

The devices were measured at room temperature on a wafer prober. Sinusoidal clock and input signals were supplied by synthesized signal generators. The output waveform of the ternary quantizer is shown in Fig. 4. A three-valued output waveform is observed at a clock signal of 10 GHz and an input signal of 1 GHz. Figure 5 plots the measured output waveforms for the 2-bit analog-to-digital converter for a clock signal of 5 GHz and input signal of 400 MHz with an amplitude of 0.5 V and centered at -3 V. Return-to-zero type 2-bit Gray code output was successfully confirmed. The lower operation frequency (5 GHz) of the ADC compared with that of the quantizer (10 GHz) is probably caused

by the encoder circuits. There is still much room to improve the encoder circuit configuration for better performance.

#### 4. CONCLUSION

We described an analog-to-digital converter that uses ternary quantizers consisting of RTDs and HEMTs. The experimental results were presented, and the ternary quantizer was shown to operate at 10 GHz, while the 2-bit ADC operated at 5 GHz.

#### ACKNOWLEDGMENTS

We would like to thank Koichi Maezawa for discussions throughout this work, Tomoyuki Akeyoshi and Ryuta Sakai for device fabrication. We also thank Yoshihiro Imamura and Kimiyoshi Yamasaki for their encouragement.

#### REFERENCES

- [1] W. Williamson III et al., "12 GHz Clocked Operation of Ultralow Power Interband Resonant Tunneling Diode Pipelined Logic Gates" IEEE J. Solid-State Circuits, vol. 32, no. 2, pp. 222-231, 1997.

- [2] K. Maezawa et al., "High-speed operation of resonant tunneling flip-flop circuit employing MOBILE", Electron Lett. Vol. 33, pp. 1733-1734, 1997.

- [3] T. P. E. Broekaert et al., "A Monolithic 4 Bit 2 GSps Resonant Tunneling Analog-to-Digital Converter", 19th GaAs IC symposium, Tech. Dig. 1997, pp. 187, 1997.

- [4] N. Shimizu et al., "In<sub>0.53</sub>Ga<sub>0.47</sub>As /AlAs resonant tunneling diodes with switching time of 1.5 ps", Electron Lett., vol. 31, no. 19, pp. 1695-1697, 1995.

- [5] S. -J. Wei, H. C. Lin, R. C. Potter and D. Shupe, "A self-latching A/D converter using resonant tunneling diodes," IEEE J. Solid-State Circuits, vol. 28, no. 6, pp.697-700, June 1993.

- [6] T. Waho, K. J. Chen, and M. Yamamoto, "A Novel Functional Logic Circuit Using Resonant-Tunneling Devices for Multiple-Valued Logic Applications", Jpn. J. Appl. Phys. vol. 36, pp. 1818-1821, 1997.

- [7] T. Waho, T. Itoh, K. Maezawa, and M. Yamamoto, "Multi-GHz A/D Converter using Resonant-Tunneling Multiple-Valued Logic Circuits", in 1998 ISSCC Dig. Tech. Papers, pp. 258-259.

- [8] K. J. Chen, K. Maezawa, T. Waho, and M. Yamamoto "Device technology for monolithic integration of InP-based resonant tunneling diodes and HEMTs", IEICE Trans. Electron., vol. E79-C, no.11, pp.1515-1524, 1996.

- [9] J. Osaka, K. Maezawa, H. Yokoyama, and M. Yamamoto, "Highly uniform regrown In<sub>0.53</sub>Ga<sub>0.47</sub>As/AlAs/InAs resonant tunneling diodes on In<sub>0.53</sub>Ga<sub>0.47</sub>As" to be presented in 10th International Conference on InP and Related Materials, 1998.